La fundición de chips más grande del mundo, TSMC, está a punto de iniciar la producción en masa de chips de última generación utilizando su nodo de proceso de 3 nm. Para decirlo en términos simples, a medida que disminuye la cantidad de nodos de proceso, los transistores utilizados para construir estos circuitos integrados se vuelven más pequeños, lo que permite que quepan más dentro de un espacio pequeño y denso como un chip. Y cuantos más transistores tiene un chip, más potente y energéticamente eficiente es.

Por ejemplo, el A13 Bionic utilizado para alimentar la serie iPhone 11 de 2019 se fabricó con el nodo de proceso mejorado de 7nm de TSMC. Ese SoC llevaba 8.500 millones de transistores. El A16 Bionic de este año fue fabricado por TSMC utilizando su nodo de proceso de 4 nm y tiene casi 16 mil millones de transistores. Se espera que el A17 Bionic del próximo año salga de las líneas de ensamblaje de TSMC después de haber sido construido con el nodo de proceso de 3 nm mejorado de TSMC (volveremos a eso pronto).

Se espera que el iPhone 15 Pro y el iPhone 15 Ultra cuenten con el chipset A17 Bionic de 3nm

Apple es el mayor cliente de TSMC y es responsable del 25% de los ingresos de la empresa. Digitimes (a través de MacRumors) escribe que se espera que TSMC comience la producción en masa de componentes utilizando el nodo de proceso de 3nm esta semana; Antes de que el A17 Bionic llegue al iPhone 15 Pro y al iPhone 15 Ultra, Apple puede colocar su chip M2 Pro de 3 nm en el MacBook Pro y el Mac Mini.

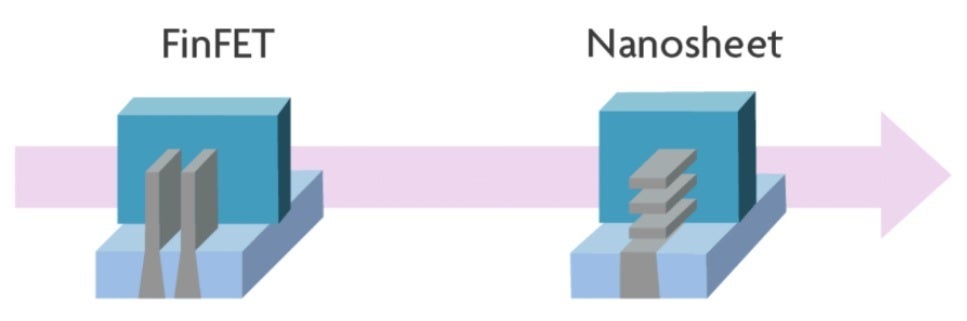

Los chips de 3nm de TSMC seguirán usando transistores FinFET (izquierda) mientras que los chips de 3nm de Samsung usarán GAA

Este jueves, se espera que TSMC marque el inicio de la producción en masa de 3 nm mediante la celebración de una ceremonia en Fab 18 en el Parque Científico del Sur de Taiwán. En el evento, TSMC discutirá sus planes para expandir la producción de 3nm en esa fábula. Se espera que el chip A17 Bionic y el chip M3 se envíen a fines del próximo año, ya que se construyeron utilizando el nodo de proceso mejorado de 3 nm de TSMC.

La única otra fundición en el mundo actualmente capaz de producir 3nm en masa es Samsung Foundry. Este último utiliza transistores gate-all-around (GAA) que permiten un control más preciso del flujo de corriente a través de cada transistor. Esto se logra haciendo que las compuertas (que se encienden y apagan para permitir o bloquear el flujo de corriente) contacten los canales en todos los lados. Con GAA, se mejora la eficiencia energética. En pocas palabras, los chips que usan transistores GAA funcionan más rápido y consumen menos energía que los chips que usan transistores FinFET.

Samsung usará transistores GAA con su producción de 3nm; TSMC seguirá con FinFET hasta que alcance la producción de 2nm

Si bien Samsung usa GAA para sus chips de 3 nm, TSMC no lo usará hasta que alcance la producción de 2 nm, lo que podría ser en 2025. TSMC continuará empleando transistores FinFET en sus chips de 3 nm que cubren solo tres lados del canal. La principal diferencia entre FinFET y GAA es que el primero utiliza “aletas” colocadas horizontalmente para aumentar el flujo de electricidad. Sin embargo, con GAA, se utilizan nanoláminas apiladas verticalmente. La colocación de las nanoláminas anchas también reduce la corriente de fuga (por lo que requiere menos energía) y mejora la corriente de accionamiento.

Entonces, ¿qué pasará después de 3 nm?

Al ayudar con la búsqueda de Intel para derrocar a TSMC y Samsung Foundry, será la primera fundición en poseer el producto de litografía ultravioleta extrema (EUV) de próxima generación de ASML, la máquina de litografía ultravioleta extrema de alta apertura numérica. ASML es responsable de fabricar y vender todas las máquinas litográficas EUV del planeta.

Las nuevas máquinas de litografía permitirán a las fundiciones grabar diseños de circuitos a resoluciones más altas para permitir características de chip 1,7 veces más pequeñas y una densidad de chip 2,9 veces mayor. Esto ayudará a Intel a grabar patrones de circuitos extremadamente finos en obleas, lo que permitirá la colocación de miles de millones de transistores adicionales dentro de un chip.

MiReal.me MiReal.me – Tu blog tecnológico con la más actualizada información

MiReal.me MiReal.me – Tu blog tecnológico con la más actualizada información